以下文章来源于高分子科技 ,作者老酒高分子

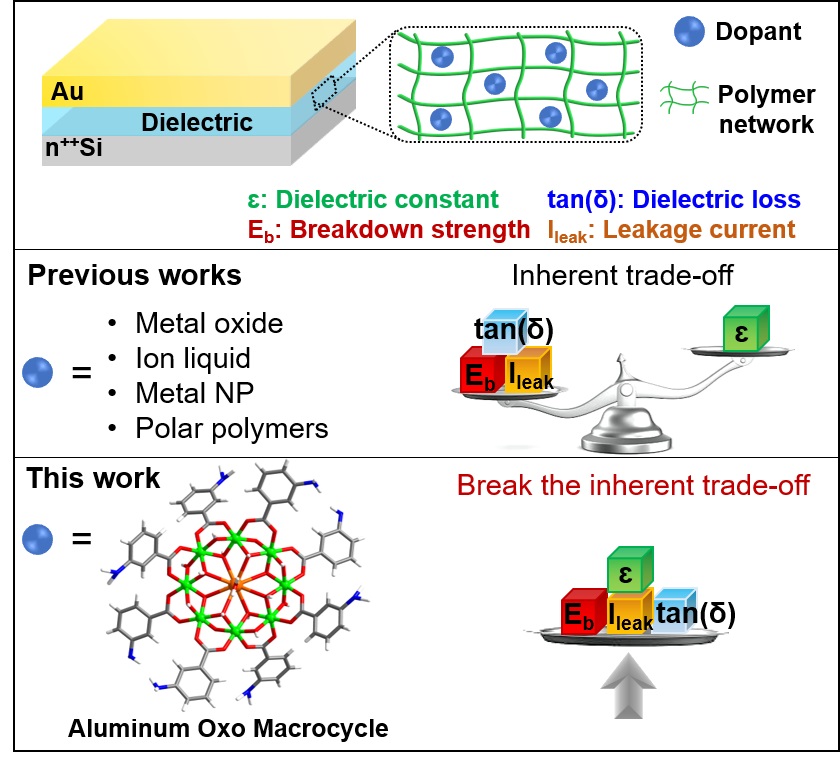

场效应晶体管(FET)是CPU、传感器和显示器的核心部件,其中,介电层对调节晶体管的整体性能方面具有至关重要的作用。目前,电介质材料仍然存在多种缺点,比如具有强偶极子耦合的铁电材料或极性聚合物电介质中的高极性基团在高电场下表现出明显的极化滞后,导致器件的高损耗。具有高介电常数的纳米颗粒添加剂虽可有效提高聚合物薄膜的电容,但同时也会增加漏电损耗并降低介电层的击穿强度。因此,聚合物介电常数和损耗之间的内在平衡已经严重阻碍了高性能聚合物介电材料的发展。

聚合物电介质设计策略的比较

中国科学院福建物质结构研究所团队提出了一种新的解决方案,即设计一种单分散的圆盘状Ce-Al-O(Ce@AlM-4)大环作为聚合物介质中的掺杂剂。由于Ce@AlM-4的三价离子特性,掺杂后的聚合物薄膜相对介电常数增大可高达7倍(k ~ 21 @ 20 Hz);此外,Ce@AlM-4具有良好的电荷散射和俘获能力,以及巨大的分子尺寸(~ 2nm),可有效的降低漏电密度和介电损耗,并提高击穿强度。另外,Ce@AlM-4丰富的外围苯基以及彼此之间的静电斥力,使Ce@AlM-4可以很好地分散在聚合物基体中,最大程度的消除了缺陷位点,进一步增强击穿强度。基于上述优点,掺杂Ce@AlM-4的聚合物介电材料所构筑的场效应晶体管在保持低泄漏电流水平的同时,提供近三个数量级的源漏电流增量,从而获得更高的电荷载流子迁移率(高达2.45 cm2V-1s-1)和开/关比。这项工作成功地打破了聚合物介电常数和损耗之间的内在平衡,为聚合物复合介电材料提供了一种独特的设计思路。该成果以“Breaking the Trade-Off Between Polymer Dielectric Constant and Loss via Aluminum Oxo Macrocycle Dopants for High-Performance Neuromorphic Electronics”为题,近期发表于Advanced Materials。福建物质结构研究所与福州大学联培硕士研究生陈晓伟、孙逸凡和中科院福建物构所博士研究生吴孝嵩为本文共同第一作者。方伟慧研究员和黄伟国研究员为本文的通讯作者。

原文链接:

https://onlinelibrary.wiley.com/doi/10.1002/adma.202306260